### ECE 331 – Digital System Design

#### Multiplexers, Decoders and Encoders

(Lecture #16)

The slides included herein were taken from the materials accompanying *Fundamentals of Logic Design*, 6<sup>th</sup> *Edition*, by Roth and Kinney, and were used with permission from Cengage Learning.

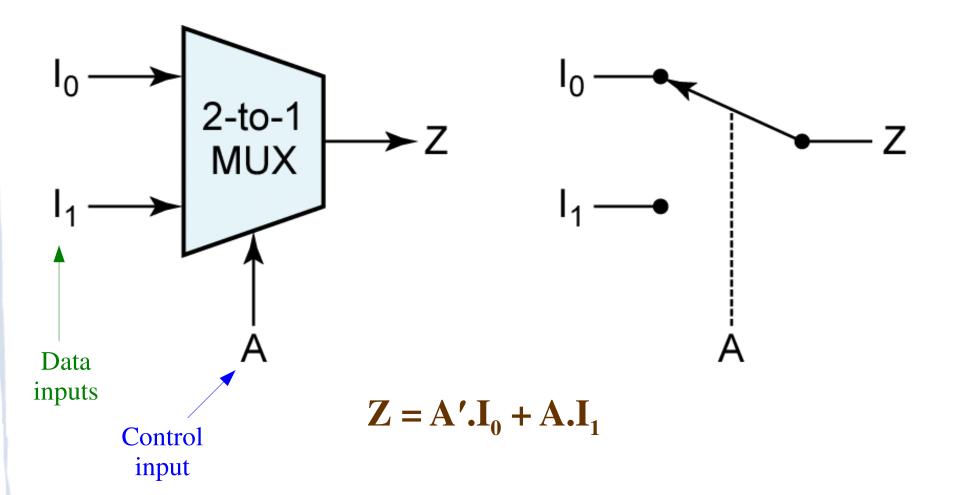

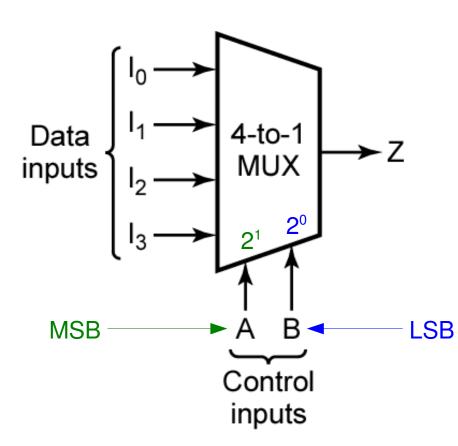

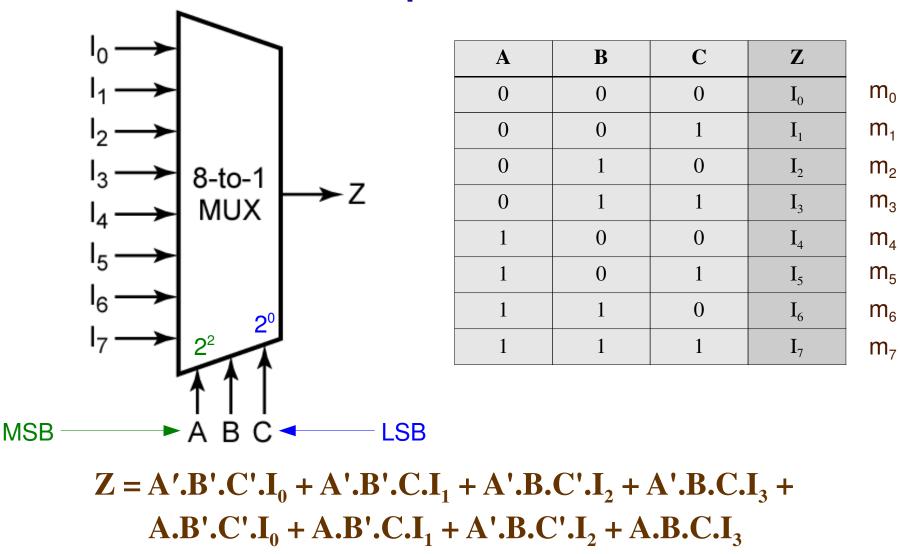

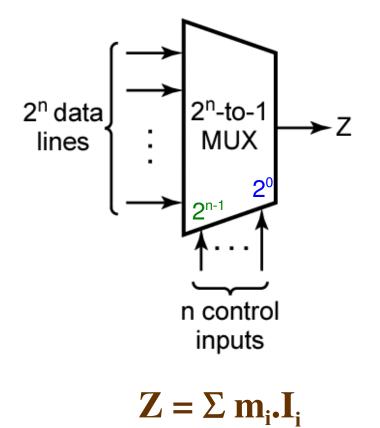

- A multiplexer has

- 2<sup>n</sup> data inputs

- n control inputs

- 1 output

- A multiplexer routes (or connects) the selected data input to the output.

- The value of the control inputs determines the data input that is selected.

| Α | В | Ζ              |

|---|---|----------------|

| 0 | 0 | $I_0$          |

| 0 | 1 | I <sub>1</sub> |

| 1 | 0 | I <sub>2</sub> |

| 1 | 1 | I <sub>3</sub> |

$m_0 = A'.B'$   $m_1 = A'.B$   $m_2 = A.B'$  $m_3 = A.B$

$Z = A'.B'.I_0 + A'.B.I_1 + A.B'.I_2 + A.B.I_3$

#### Multiplexers in VHDL

### 8-to-1 Multiplexer

```

entity Multiplexer_8to1 is

Port ( I : in STD_LOGIC_VECTOR (7 downto 0);

sel : in STD_LOGIC_VECTOR (2 downto 0);

Z : out STD_LOGIC);

end Multiplexer_8to1;

```

architecture Bool\_Exp of Multiplexer\_8to1 is

begin

```

Z <= ( not(sel(2)) and not(sel(1)) and not(sel(0)) and I(0) ) or

( not(sel(2)) and not(sel(1)) and sel(0) and I(1) ) or

( not(sel(2)) and sel(1) and not(sel(0)) and I(2) ) or

( not(sel(2)) and sel(1) and sel(0) and I(3) ) or

( sel(2) and not(sel(1)) and not(sel(0)) and I(4) ) or

( sel(2) and not(sel(1)) and sel(0) and I(5) ) or

( sel(2) and sel(1) and not(sel(0)) and I(6) ) or

( sel(2) and sel(1) and sel(0) and I(7) );

```

end Bool\_Exp;

### 8-to-1 Multiplexer

```

entity Multiplexer_8to1_2 is

Port ( I : in STD_LOGIC_VECTOR (7 downto 0);

sel : in STD_LOGIC_VECTOR (2 downto 0);

Z : out STD_LOGIC);

end Multiplexer_8to1_2;

```

architecture Truth\_Table of Multiplexer\_8to1\_2 is

begin

with sel select

```

Z <= I(7) when "111",

I(6) when "110",

I(5) when "101",

I(4) when "100",

I(3) when "011",

I(2) when "010",

I(1) when "001",

I(0) when "000",

I(0) when others;

```

end Truth\_Table;

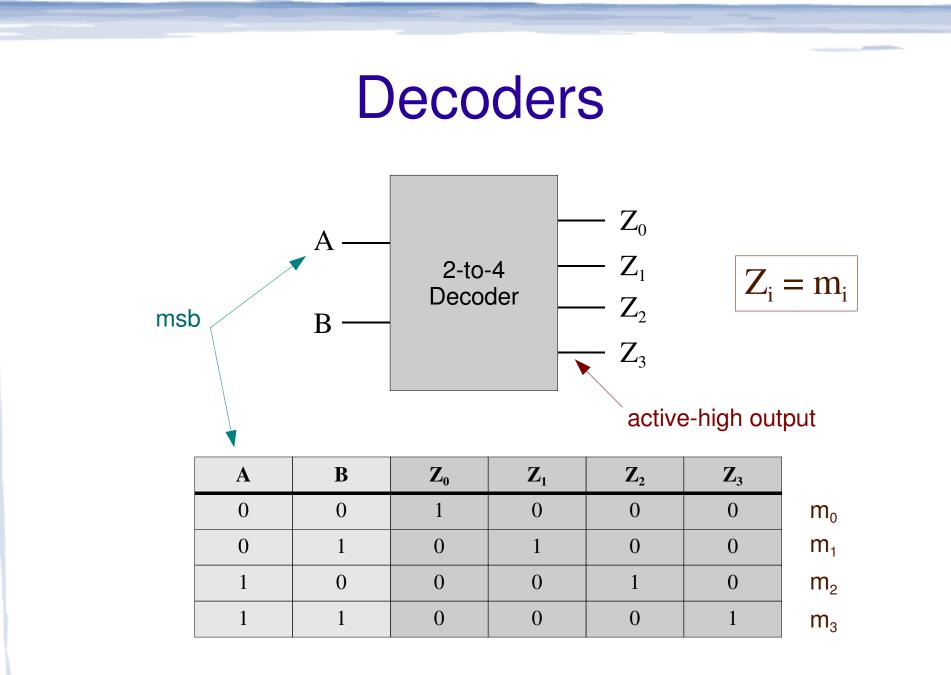

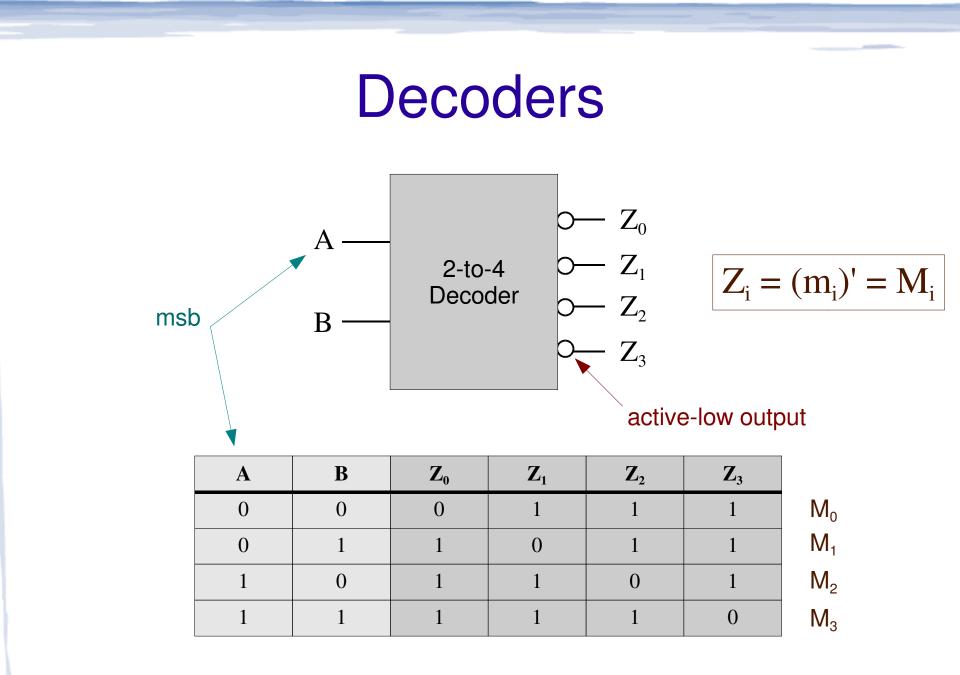

#### Decoders

#### Decoders

- A decoder has

- *n* inputs

- 2<sup>n</sup> outputs

- A decoder selects one of 2<sup>n</sup> outputs by decoding the binary value on the *n* inputs.

- The decoder generates all of the minterms of the *n* input variables.

Exactly one output will be active for each combination of the inputs.

What does "active" mean?

#### Decoders

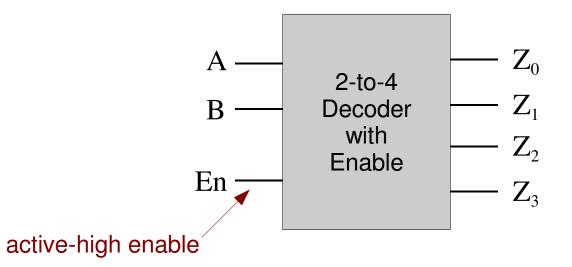

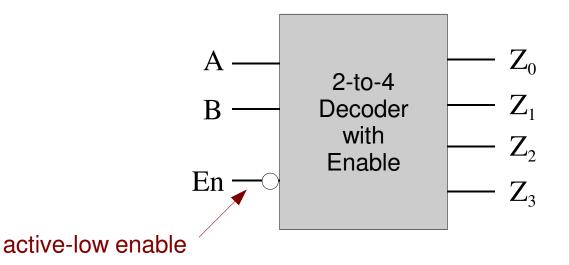

#### **Decoder with Enable**

|          | En | Α | В | $\mathbf{Z}_{0}$ | $\mathbf{Z}_1$ | $\mathbf{Z}_2$ | <b>Z</b> <sub>3</sub> |

|----------|----|---|---|------------------|----------------|----------------|-----------------------|

|          | 1  | 0 | 0 | 1                | 0              | 0              | 0                     |

| enabled  | 1  | 0 | 1 | 0                | 1              | 0              | 0                     |

|          | 1  | 1 | 0 | 0                | 0              | 1              | 0                     |

|          | 1  | 1 | 1 | 0                | 0              | 0              | 1                     |

| disabled | 0  | Х | Х | 0                | 0              | 0              | 0                     |

#### **Decoder with Enable**

|          | En | Α | В | $\mathbf{Z}_{0}$ | $\mathbf{Z}_1$ | $\mathbf{Z}_2$ | $Z_3$ |

|----------|----|---|---|------------------|----------------|----------------|-------|

| enabled  | 0  | 0 | 0 | 1                | 0              | 0              | 0     |

|          | 0  | 0 | 1 | 0                | 1              | 0              | 0     |

|          | 0  | 1 | 0 | 0                | 0              | 1              | 0     |

|          | 0  | 1 | 1 | 0                | 0              | 0              | 1     |

| disabled | 1  | Х | Х | 0                | 0              | 0              | 0     |

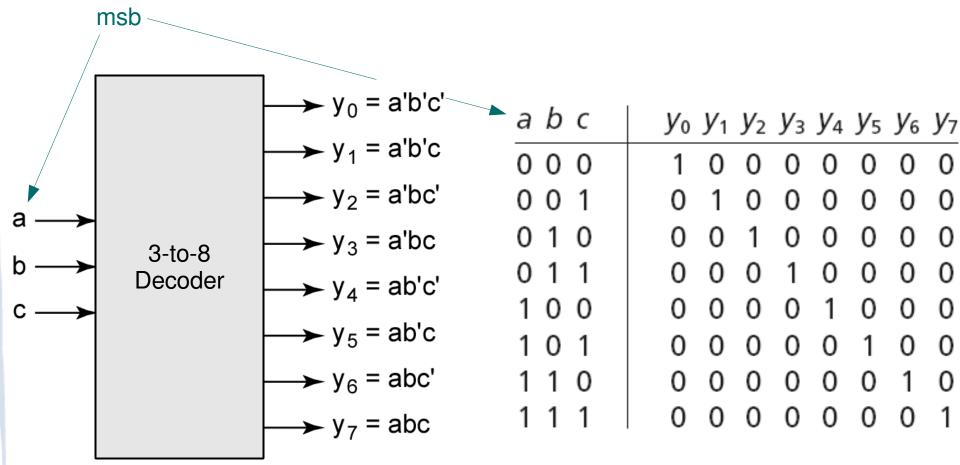

#### Decoders in VHDL

#### 3-to-8 Decoder

```

entity Decoder_3to8_1 is

Port ( I : in STD_LOGIC_VECTOR (2 downto 0);

Z : out STD_LOGIC_VECTOR (7 downto 0) );

end Decoder_3to8_1;

```

architecture Boolean\_Expression of Decoder\_3to8\_1 is

begin

Z(0) <= ( not(I(2)) and not(I(1)) and not(I(0)) ); Z(1) <= ( not(I(2)) and not(I(1)) and I(0) ); Z(2) <= ( not(I(2)) and I(1) and not(I(0)) ); Z(3) <= ( not(I(2)) and I(1) and I(0) ); Z(4) <= ( I(2) and not(I(1)) and not(I(0)) ); Z(5) <= ( I(2) and not(I(1)) and I(0) ); Z(6) <= ( I(2) and I(1) and not(I(0)) ); Z(7) <= ( I(2) and I(1) and I(0) );</pre>

end Boolean\_Expression;

#### 3-to-8 Decoder

```

entity Decoder_3to8_2 is

Port ( I : in STD_LOGIC_VECTOR (2 downto 0);

Z : out STD_LOGIC_VECTOR (7 downto 0));

end Decoder_3to8_2;

```

architecture Truth\_Table of Decoder\_3to8\_2 is

begin

with I select

| Ζ | <= | "10000000" | when | "111",  |

|---|----|------------|------|---------|

|   |    | "01000000" | when | "110",  |

|   |    | "00100000" | when | "101",  |

|   |    | "00010000" | when | "100",  |

|   |    | "00001000" | when | "011",  |

|   |    | "00000100" | when | "010",  |

|   |    | "00000010" | when | "001",  |

|   |    | "00000001" | when | "000",  |

|   |    | "00000000" | when | others; |

end Truth\_Table;

#### 2-to-4 Decoder with Enable

```

entity Decoder_2to4_withEN is

Port ( I : in STD_LOGIC_VECTOR (1 downto 0);

Z : out STD_LOGIC_VECTOR (3 downto 0);

En : in STD_LOGIC);

end Decoder_2to4_withEN;

```

architecture Truth\_Table of Decoder\_2to4\_withEN is signal EnabledInput : STD\_LOGIC\_VECTOR (2 downto 0);

begin

```

EnabledInput <= En & I; -- concatenate the En signal

-- with the data inputs (I)

```

with EnabledInput select

```

Z <= "1000" when "111",

"0100" when "110",

"0010" when "101",

"0001" when "100",

"0000" when "000",

"0000" when others;

```

end Truth Table:

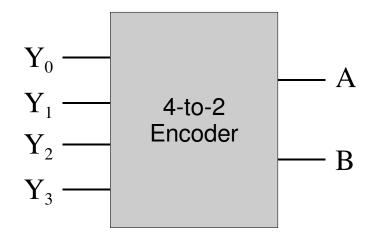

#### Encoders

- An encoder has

- 2<sup>n</sup> inputs

- n outputs

- Outputs the binary value of the selected (or active) input.

- Performs the inverse operation of a decoder.

- Issues

- What if more than one input is active?

- What if no inputs are active?

#### Encoders

| Y <sub>0</sub> | Y <sub>1</sub> | Y <sub>2</sub> | Y <sub>3</sub> | Α | В |

|----------------|----------------|----------------|----------------|---|---|

| 1              | 0              | 0              | 0              | 0 | 0 |

| 0              | 1              | 0              | 0              | 0 | 1 |

| 0              | 0              | 1              | 0              | 1 | 0 |

| 0              | 0              | 0              | 1              | 1 | 1 |

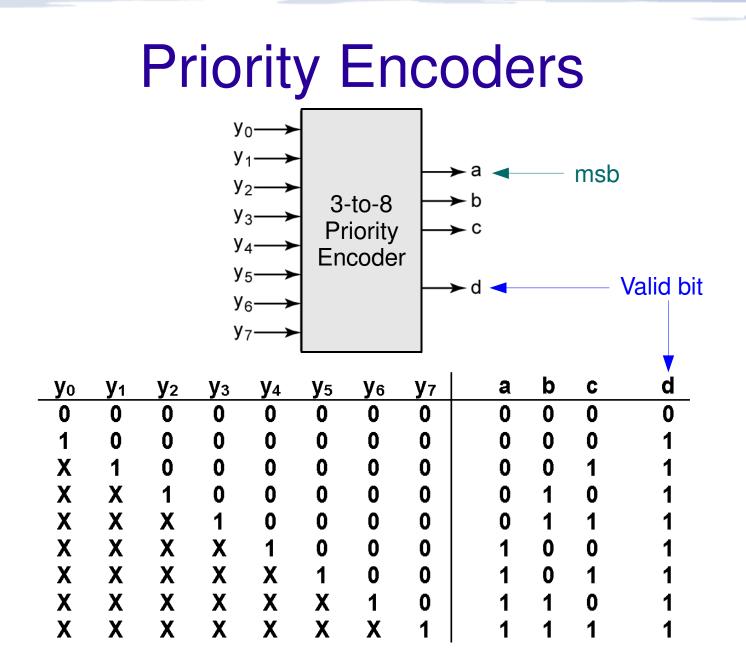

# **Priority Encoders**

- If more than one input is active, the higher-order input has priority over the lower-order input.

- The higher value is encoded on the output

- A valid indicator, d, is included to indicate whether or not the output is valid.

- Output is invalid when no inputs are active

• d = 0

Output is valid when at least one input is active

d = 1

Why is the valid indicator needed?

#### Encoders in VHDL

### 4-to-2 Priority Encoder

LIBRARY ieee ; USE ieee.std\_logic\_1164.all ;

4 input bits

ENTITY priority IS PORT (w : IN STD\_LOGIC\_VECTOR(3 DOWNTO 0); y : OUT STD LOGIC VECTOR(1 DOWNTO 0);

$z = : OUT STD_LOGIC );$

END priority;

valid indicator

2 output bits

ARCHITECTURE Behavior OF priority IS BEGIN

```

y <= "11" WHEN w(3) = '1' ELSE

"10" WHEN w(2) = '1' ELSE

"01" WHEN w(1) = '1' ELSE

```

Active-high inputs and outputs

```

"00" ;

z <= '0' WHEN w = "0000" ELSE '1' ;

END Behavior ;

```

#### Circuit Design using <u>Multiplexers</u>

## Using a <u>2<sup>n</sup>-input</u> Multiplexer

- Use a 2<sup>n</sup>-input multiplexer to realize a logic circuit for a function with 2<sup>n</sup> minterms.

- n = # of control inputs = # of variables in the function

- Each minterm of the function can be mapped to a data input of the multiplexer.

- For each row in the truth table, for the function, where the output is 1, set the corresponding data input of the multiplexer to 1.

- That is, for each minterm in the minterm expansion of the function, set the corresponding input of the multiplexer to 1.

- Set the remaining inputs of the multiplexer to 0.

### Using an <u>2<sup>n</sup>-input</u> Mux

Example:

Using an 8-to-1 multiplexer, design a logic circuit to realize the following Boolean function

$F(A,B,C) = \Sigma m(2, 3, 5, 6, 7)$

### Using an <u>2<sup>n</sup>-input</u> Mux

Example:

Using an 8-to-1 multiplexer, design a logic circuit to realize the following Boolean function

$F(A,B,C) = \Sigma m(1, 2, 4)$

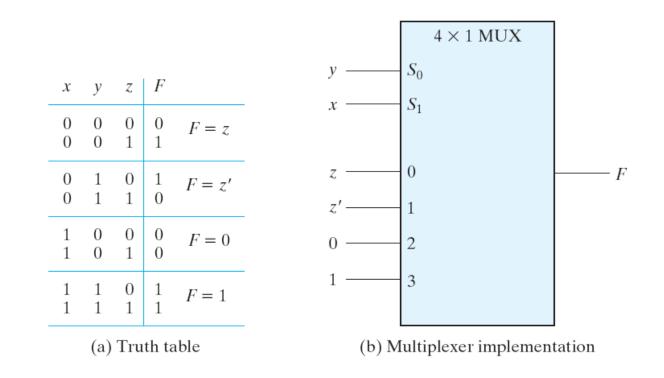

# Using an <u>2</u><sup>(n-1)</sup>-input Multiplexer

- Use a 2<sup>(n-1)</sup>-input multiplexer to realize a logic circuit for a function with 2<sup>n</sup> minterms.

- -n-1 = # of control inputs; n = # of variables in function

- Group the rows of the truth table, for the function, into  $2^{(n-1)}$  pairs of rows.

- Each pair of rows represents a product term of (n 1) variables.

- Each pair of rows is mapped to one data input of the mux.

- Determine the logical function of each pair of rows in terms of the remaining variable.

- If the remaining variable, for example, is x, then the

# Using an <u>2</u><sup>(n-1)</sup>-input Mux

#### Example: $F(x,y,z) = \Sigma m(1, 2, 6, 7)$

## Using an <u>2</u><sup>(n-1)</sup>-input Mux

#### Example: $F(A,B,C,D) = \Sigma m(1,3,4,11,12-15)$

| A B C D F                                            |                                                                                                           |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $8 \times 1 \mathrm{MUX}$                                                                                 |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c} C \\ B \\ \hline \end{array} \\ \hline \end{array} \\ \hline S_1 \\ \hline \end{array}$ |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | $\begin{array}{c} A \\ \hline \\ D \\ \hline \\ \end{array} \\ 0 \\ \end{array} \\ 0 \\ \end{array}$      |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                                                                                                           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                                                                                                           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                                                                                                           |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ | 7                                                                                                         |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |                                                                                                           |

# Using a <u>2</u><sup>(n-2)</sup>-input Mux

A similar design approach can be implemented using a  $2^{(n-2)}$ -input multiplexer.

#### Circuit Design using <u>Decoders</u>

## Using an <u>*n*-output</u> Decoder

- Use an *n*-output decoder to realize a logic circuit for a function with *n* minterms.

- Each minterm of the function can be mapped to an output of the decoder.

- For each row in the truth table, for the function, where the output is 1, sum (or "OR") the corresponding outputs of the decoder.

- That is, for each minterm in the minterm expansion of the function, OR the corresponding outputs of the decoder.

- Leave remaining outputs of the decoder unconnected.

#### Using an <u>*n*-output</u> Decoder

Example:

Using a 3-to-8 decoder, design a logic circuit to realize the following Boolean function

$F(A,B,C) = \Sigma m(2, 3, 5, 6, 7)$

#### Using an <u>*n*-output</u> Decoder

Example:

Using two 2-to-4 decoders, design a logic circuit to realize the following Boolean function

$F(A,B,C) = \Sigma m(0, 1, 4, 6, 7)$

- Several issues arise when designing large multiplexers and decoders (as 2-level circuits).

- Number of logic gates gets prohibitively large

- Number of inputs to each logic gate (i.e. fan-in) gets prohibitively large

- Instead, design both hierarchically

- Use smaller elements as building blocks

- Interconnect building blocks in a multi-tier structure

#### Exercise:

# Design an 8-to-1 multiplexer using 4-to-1 and 2-to-1 multiplexers only.

#### Exercise:

# Design a 16-to-1 multiplexer using 4-to-1 multiplexers only.

#### Exercise:

# Design a 4-to-16 decoder using 2-to-4 decoders only.

#### Questions?