Since  $R_C$  is always considerably larger in value than  $r'_e$ , the output voltage for this configuration is greater than the input voltage. Various types of amplifiers are covered in detail in later chapters.

|  | SECTION 4-4 | . What is amplification?                                                                                                     |

|--|-------------|------------------------------------------------------------------------------------------------------------------------------|

|  | СНЕСКИР 2   | . How is voltage gain defined?                                                                                               |

|  | 3           | Name two factors that determine the voltage gain of an amplifier.                                                            |

|  | 4           | . What is the voltage gain of a transistor amplifier that has an output of 5 V rms and an input of 250 mV rms?               |

|  | 5           | A transistor connected as in Figure 4–22 has an $r'_e = 20 \ \Omega$ . If $R_C$ is 1200 $\Omega$ , what is the voltage gain? |

# 4–5 THE BJT AS A SWITCH

In the previous section, you saw how a BJT can be used as a linear amplifier. The second major application area is switching applications. When used as an electronic switch, a BJT is normally operated alternately in cutoff and saturation. Many digital circuits use the BJT as a switch.

After completing this section, you should be able to

- Discuss how a BJT is used as a switch

- Describe BJT switching operation

- Explain the conditions in cutoff

- Determine the cutoff voltage in terms of the dc supply voltage

• Explain the conditions in saturation

- Calculate the collector current and the base current in saturation

- Describe a simple application

## **Switching Operation**

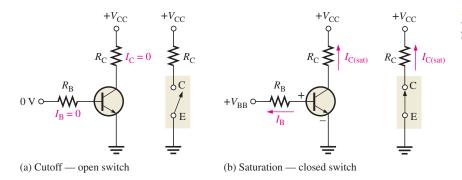

Figure 4–23 illustrates the basic operation of a BJT as a switching device. In part (a), the transistor is in the cutoff region because the base-emitter junction is not forward-biased. In this condition, there is, ideally, an *open* between collector and emitter, as indicated by the switch equivalent. In part (b), the transistor is in the saturation region because the base-emitter junction and the base-collector junction are forward-biased and the base current is made large enough to cause the collector current to reach its saturation value. In this condition, there is, ideally, a *short* between collector and emitter, as indicated by the switch equivalent. Actually, a *short* between collector and emitter, as indicated by the switch equivalent. Actually, a small voltage drop across the transister of up to a few tenths of a volt normally occurs, which is the saturation voltage,  $V_{CE(sat)}$ .

#### FIGURE 4–23

Switching action of an ideal transistor.

**Conditions in Cutoff** As mentioned before, a transistor is in the cutoff region when the base-emitter junction is not forward-biased. Neglecting leakage current, all of the currents are zero, and  $V_{CE}$  is equal to  $V_{CC}$ .

$$V_{\text{CE(cutoff)}} = V_{\text{CC}}$$

Equation 4–8

**Conditions in Saturation** As you have learned, when the base-emitter junction is forward-biased and there is enough base current to produce a maximum collector current, the transistor is saturated. The formula for collector saturation current is

$$I_{C(sat)} = \frac{V_{CC} - V_{CE(sat)}}{R_C}$$

Equation 4–9

Since  $V_{CE(sat)}$  is very small compared to  $V_{CC}$ , it can usually be neglected.

The minimum value of base current needed to produce saturation is

$$I_{\rm B(min)} = \frac{I_{\rm C(sat)}}{\beta_{\rm DC}}$$

Equation 4–10

Normally,  $I_{\rm B}$  should be significantly greater than  $I_{\rm B(min)}$  to ensure that the transistor is saturated.

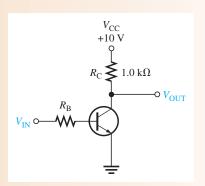

| EXAMPLE 4–10 | (a) For the transistor circuit in Figure 4–24, what is $V_{CE}$ when $V_{IN} = 0$ V?                                                     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------|

|              | (b) What minimum value of $I_{\rm B}$ is required to saturate this transistor if $\beta_{\rm DC}$ is 200?<br>Neglect $V_{\rm CE(sat)}$ . |

|              | (c) Calculate the maximum value of $R_{\rm B}$ when $V_{\rm IN} = 5$ V.                                                                  |

### FIGURE 4–24

Solution (a) When  $V_{\rm IN} = 0$  V, the transistor is in cutoff (acts like an open switch) and

$$V_{\rm CE} = V_{\rm CC} = 10 \, {\rm V}$$

(b) Since  $V_{CE(sat)}$  is neglected (assumed to be 0 V),

$$I_{\rm C(sat)} = \frac{V_{\rm CC}}{R_{\rm C}} = \frac{10 \text{ V}}{1.0 \text{ k}\Omega} = 10 \text{ mA}$$

$$I_{\rm B(min)} = \frac{I_{\rm C(sat)}}{\beta_{\rm DC}} = \frac{10 \text{ mA}}{200} = 50 \ \mu \text{A}$$

This is the value of  $I_{\rm B}$  necessary to drive the transistor to the point of saturation. Any further increase in  $I_{\rm B}$  will ensure the transistor remains in saturation but there cannot be any further increase in  $I_{\rm C}$ .

(c) When the transistor is on,  $V_{\rm BE} \approx 0.7$  V. The voltage across  $R_{\rm B}$  is

$$V_{R_{\rm P}} = V_{\rm IN} - V_{\rm BE} \cong 5 \,\rm V - 0.7 \,\rm V = 4.3 \,\rm V$$

Calculate the maximum value of  $R_{\rm B}$  needed to allow a minimum  $I_{\rm B}$  of 50  $\mu$ A using Ohm's law as follows:

$$R_{\rm B(max)} = \frac{V_{R_{\rm B}}}{I_{\rm B(min)}} = \frac{4.3 \,\mathrm{V}}{50 \,\mu\mathrm{A}} = 86 \,\mathrm{k}\Omega$$

**Related Problem**

Determine the minimum value of  $I_{\rm B}$  required to saturate the transistor in Figure 4–24 if  $\beta_{\rm DC}$  is 125 and  $V_{\rm CE(sat)}$  is 0.2 V.

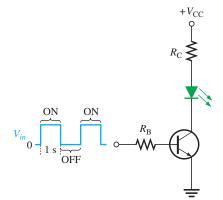

## A Simple Application of a Transistor Switch

The transistor in Figure 4-25 is used as a switch to turn the LED on and off. For example, a square wave input voltage with a period of 2 s is applied to the input as indicated. When

## FIGURE 4–25 A transistor used to switch an LED on and off.

# 5-1 THE DC OPERATING POINT

A transistor must be properly biased with a dc voltage in order to operate as a linear amplifier. A dc operating point must be set so that signal variations at the input terminal are amplified and accurately reproduced at the output terminal. As you learned in Chapter 4, when you bias a transistor, you establish the dc voltage and current values. This means, for example, that at the dc operating point,  $I_C$  and  $V_{CE}$  have specified values. The dc operating point is often referred to as the Q-point (quiescent point).

After completing this section, you should be able to

- Discuss and determine the dc operating point of a linear amplifier

- Explain the purpose of dc bias

- Define *Q-point* and describe how it affects the output of an amplifier

Explain how collector characteristic curves are produced

Describe and draw a dc load line

State the conditions for linear operation

Explain what causes waveform distortion

## **DC Bias**

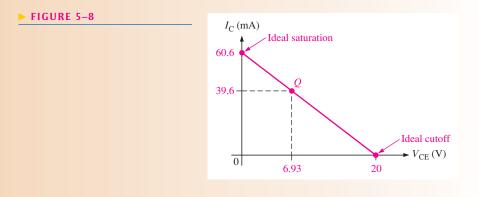

Bias establishes the dc operating point (**Q-point**) for proper linear operation of an amplifier. If an amplifier is not biased with correct dc voltages on the input and output, it can go into saturation or cutoff when an input signal is applied. Figure 5–1 shows the effects of proper and improper dc biasing of an inverting amplifier. In part (a), the output signal is an amplified replica of the input signal except that it is inverted, which means that it is 180° out of phase with the input. The output signal swings equally above and below the dc bias level of the output,  $V_{\text{DC(out)}}$ . Improper biasing can cause distortion in the output signal, as illustrated in parts (b) and (c). Part (b) illustrates limiting of the positive portion of the output voltage as a result of a Q-point (dc operating point) being too close to cutoff. Part (c) shows limiting of the negative portion of the output voltage as a result of a dc operating point being too close to saturation.

(b) Nonlinear operation: output voltage limited (clipped) by cutoff

(a) Linear operation: larger output has same shape as input except that it is inverted

(c) Nonlinear operation: output voltage limited (clipped) by saturation

#### ▲ FIGURE 5-1

Examples of linear and nonlinear operation of an inverting amplifier (the triangle symbol).

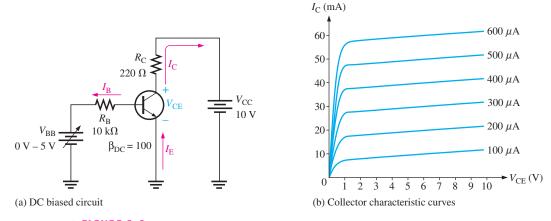

**Graphical Analysis** The transistor in Figure 5–2(a) is biased with  $V_{CC}$  and  $V_{BB}$  to obtain certain values of  $I_B$ ,  $I_C$ ,  $I_E$ , and  $V_{CE}$ . The collector characteristic curves for this particular

transistor are shown in Figure 5–2(b); we will use these curves to graphically illustrate the effects of dc bias.

### ▲ FIGURE 5-2

A dc-biased transistor circuit with variable bias voltage ( $V_{BB}$ ) for generating the collector characteristic curves shown in part (b).

## FYI

In 1965, a single transistor cost more than a dollar. By 1975, the cost of a transistor had dropped to less than a penny, while transistor size allowed for almost 100,000 transistors on a single chip. From 1979 to 1999, processor performance went from about 1.5 million instructions per second (MIPS) to over 1,000 MIPS. Today's processors, some topping out at well above one billion transistors, run at 3.2 GHz and higher, deliver over 10,000 MIPS, and can be manufactured in high volumes with transistors that cost less than 1/10,000th of a cent.

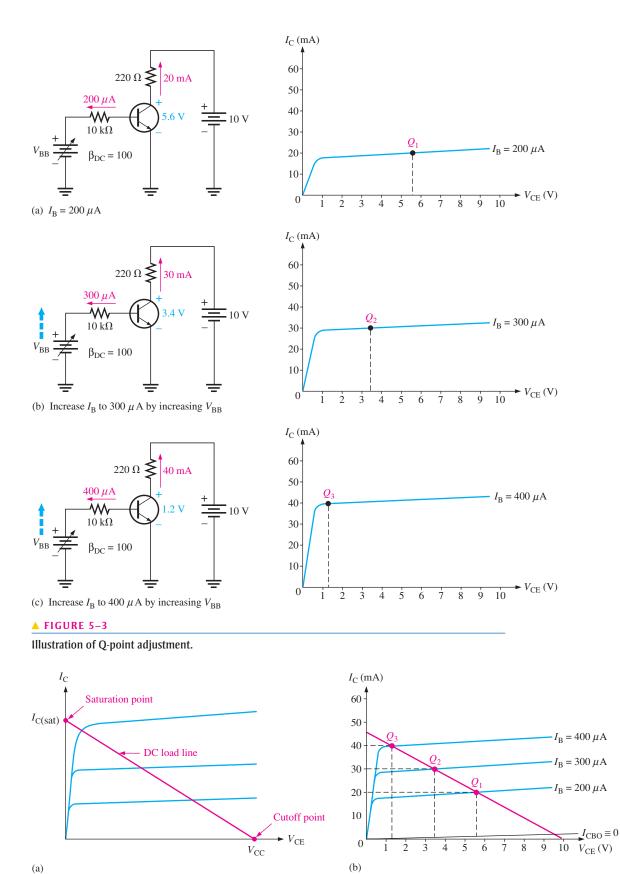

In Figure 5–3, we assign three values to  $I_{\rm B}$  and observe what happens to  $I_{\rm C}$  and  $V_{\rm CE}$ . First,  $V_{\rm BB}$  is adjusted to produce an  $I_{\rm B}$  of 200  $\mu$ A, as shown in Figure 5–3(a). Since  $I_{\rm C} = \beta_{\rm DC}I_{\rm B}$ , the collector current is 20 mA, as indicated, and

$$V_{\rm CE} = V_{\rm CC} - I_{\rm C}R_{\rm C} = 10 \,\text{V} - (20 \,\text{mA})(220 \,\Omega) = 10 \,\text{V} - 4.4 \,\text{V} = 5.6 \,\text{V}$$

This Q-point is shown on the graph of Figure 5–3(a) as  $Q_1$ .

Next, as shown in Figure 5–3(b),  $V_{BB}$  is increased to produce an  $I_B$  of 300  $\mu$ A and an  $I_C$  of 30 mA.

$$V_{\rm CE} = 10 \,\mathrm{V} - (30 \,\mathrm{mA})(220 \,\Omega) = 10 \,\mathrm{V} - 6.6 \,\mathrm{V} = 3.4 \,\mathrm{V}$$

The Q-point for this condition is indicated by  $Q_2$  on the graph.

Finally, as in Figure 5–3(c),  $V_{BB}$  is increased to give an  $I_B$  of 400  $\mu$ A and an  $I_C$  of 40 mA.

$$V_{\rm CE} = 10 \,\mathrm{V} - (40 \,\mathrm{mA})(220 \,\Omega) = 10 \,\mathrm{V} - 8.8 \,\mathrm{V} = 1.2 \,\mathrm{V}$$

$Q_3$  is the corresponding Q-point on the graph.

**DC Load Line** The dc operation of a transistor circuit can be described graphically using a **dc load line**. This is a straight line drawn on the characteristic curves from the saturation value where  $I_{\rm C} = I_{\rm C(sat)}$  on the *y*-axis to the cutoff value where  $V_{\rm CE} = V_{\rm CC}$  on the *x*-axis, as shown in Figure 5–4(a). The load line is determined by the external circuit ( $V_{\rm CC}$  and  $R_{\rm C}$ ), not the transistor itself, which is described by the characteristic curves.

In Figure 5–3, the equation for  $I_{\rm C}$  is

$$I_{\rm C} = \frac{V_{\rm CC} - V_{\rm CE}}{R_{\rm C}} = \frac{V_{\rm CC}}{R_{\rm C}} - \frac{V_{\rm CE}}{R_{\rm C}} = -\frac{V_{\rm CE}}{R_{\rm C}} + \frac{V_{\rm CC}}{R_{\rm C}} = -\left(\frac{1}{R_{\rm C}}\right)V_{\rm CE} + \frac{V_{\rm CC}}{R_{\rm C}}$$

This is the equation of a straight line with a slope of  $-1/R_{\rm C}$ , an x intercept of  $V_{\rm CE} = V_{\rm CC}$ , and a y intercept of  $V_{\rm CC}/R_{\rm C}$ , which is  $I_{\rm C(sat)}$ .

### ▲ FIGURE 5-4

The dc load line.

## FYI

Gordon Moore, one of the founders of Intel, observed in an article in the April, 1965, issue of *Electronics* magazine that innovations in technology would allow a doubling of the number of transistors in a given space every year (in an update article in 1975, Moore adjusted the rate to every two years to account for the growing complexity of chips), and that the speed of those transistors would increase. This prediction has become widely known as Moore's law. The point at which the load line intersects a characteristic curve represents the Q-point for that particular value of  $I_{\rm B}$ . Figure 5–4(b) illustrates the Q-point on the load line for each value of  $I_{\rm B}$  in Figure 5–3.

**Linear Operation** The region along the load line including all points between saturation and cutoff is generally known as the **linear region** of the transistor's operation. As long as the transistor is operated in this region, the output voltage is ideally a linear reproduction of the input.

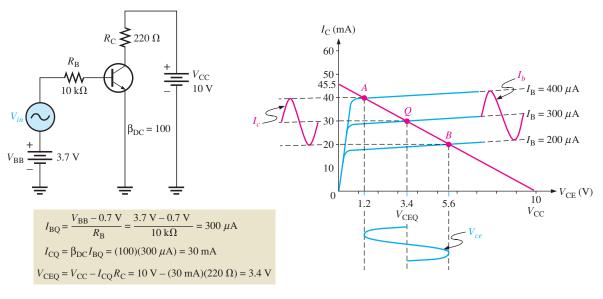

Figure 5–5 shows an example of the linear operation of a transistor. AC quantities are indicated by lowercase italic subscripts. Assume a sinusoidal voltage,  $V_{in}$ , is superimposed on  $V_{BB}$ , causing the base current to vary sinusoidally 100  $\mu$ A above and below its Q-point value of 300  $\mu$ A. This, in turn, causes the collector current to vary 10 mA above and below its Q-point value of 30 mA. As a result of the variation in collector current, the collector-to-emitter voltage varies 2.2 V above and below its Q-point value of 3.4 V. Point A on the load line in Figure 5–5 corresponds to the positive peak of the sinusoidal input voltage. Point *B* corresponds to the negative peak, and point *Q* corresponds to the zero value of the sine wave, as indicated.  $V_{CEQ}$ ,  $I_{CQ}$ , and  $I_{BQ}$  are dc Q-point values with no input sinusoidal voltage applied.

#### ▲ FIGURE 5-5

Variations in collector current and collector-to-emitter voltage as a result of a variation in base current.

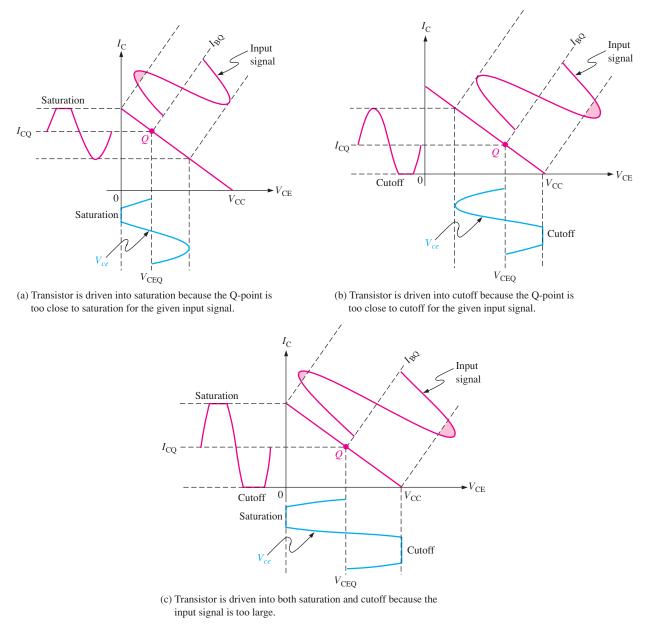

**Waveform Distortion** As previously mentioned, under certain input signal conditions the location of the Q-point on the load line can cause one peak of the  $V_{ce}$  waveform to be limited or clipped, as shown in parts (a) and (b) of Figure 5–6. In each case the input signal is too large for the Q-point location and is driving the transistor into cutoff or saturation during a portion of the input cycle. When both peaks are limited as in Figure 5–6(c), the transistor is being driven into both saturation and cutoff by an excessively large input signal. When only the positive peak is limited, the transistor is being driven into saturation at saturation. When only the negative peak is limited, the transistor is being driven into saturation but not cutoff.

#### ▲ FIGURE 5-6

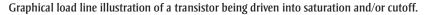

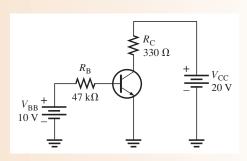

**EXAMPLE 5-1**Determine the Q-point for the circuit in Figure 5–7 and draw the dc load line. Find the<br/>maximum peak value of base current for linear operation. Assume  $\beta_{DC} = 200$ .SolutionThe Q-point is defined by the values of  $I_C$  and  $V_{CE}$ . $I_B = \frac{V_{BB} - V_{BE}}{R_B} = \frac{10 \text{ V} - 0.7 \text{ V}}{47 \text{ k}\Omega} = 198 \,\mu\text{A}$ <br/> $I_C = \beta_{DC}I_B = (200)(198 \,\mu\text{A}) = 39.6 \,\text{mA}$

$V_{\rm CE} = V_{\rm CC} - I_{\rm C}R_{\rm C} = 20 \,\rm V - 13.07 \,\rm V = 6.93 \,\rm V$

### FIGURE 5-7

The Q-point is at  $I_{\rm C} = 39.6$  mA and at  $V_{\rm CE} = 6.93$  V.

Since  $I_{C(cutoff)} = 0$ , you need to know  $I_{C(sat)}$  to determine how much variation in collector current can occur and still maintain linear operation of the transistor.

$$I_{\rm C(sat)} = \frac{V_{\rm CC}}{R_{\rm C}} = \frac{20 \,\rm V}{330 \,\Omega} = 60.6 \,\rm mA$$

The dc load line is graphically illustrated in Figure 5–8, showing that before saturation is reached,  $I_C$  can increase an amount ideally equal to

$$I_{C(sat)} - I_{CO} = 60.6 \text{ mA} - 39.6 \text{ mA} = 21.0 \text{ mA}$$

However,  $I_C$  can decrease by 39.6 mA before cutoff ( $I_C = 0$ ) is reached. Therefore, the limiting excursion is 21 mA because the *Q*-point is closer to saturation than to cutoff. The 21 mA is the maximum peak variation of the collector current. Actually, it would be slightly less in practice because  $V_{CE(sat)}$  is not quite zero.

Determine the maximum peak variation of the base current as follows:

$$I_{b(peak)} = \frac{I_{c(peak)}}{\beta_{\rm DC}} = \frac{21 \,{\rm mA}}{200} = 105 \,\mu{\rm A}$$

### **Related Problem\***

Find the Q-point for the circuit in Figure 5–7, and determine the maximum peak value of base current for linear operation for the following circuit values:  $\beta_{DC} = 100$ ,  $R_C = 1.0 \text{ k}\Omega$ , and  $V_{CC} = 24 \text{ V}$ .

\*Answers can be found at www.pearsonhighered.com/floyd.

ultisim

Open the Multisim file E05-01 in the Examples folder on the companion website. Measure  $I_{\rm C}$  and  $V_{\rm CE}$  and compare with the calculated values.

| SECTION 5–1<br>CHECKUP<br>Answers can be found at www.<br>pearsonhighered.com/floyd. | <ol> <li>What are the upper and lower limits on a dc load line in terms of V<sub>CE</sub> and I<sub>C</sub>?</li> <li>Define <i>Q-point</i>.</li> <li>At what point on the load line does saturation occur? At what point does cutoff occur?</li> <li>For maximum V<sub>ce</sub>, where should the Q-point be placed?</li> </ol> |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

# 5-2 **VOLTAGE-DIVIDER BIAS**

You will now study a method of biasing a transistor for linear operation using a singlesource resistive voltage divider. This is the most widely used biasing method. Four other methods are covered in Section 5–3.

After completing this section, you should be able to

- Analyze a voltage-divider biased circuit

- Define the term *stiff voltage-divider* Calculate currents and voltages in a voltage-divider biased circuit

- Explain the loading effects in voltage-divider bias

- Describe how dc input resistance at the transistor base affects the bias

- Apply Thevenin's theorem to the analysis of voltage-divider bias

- Analyze both npn and pnp circuits

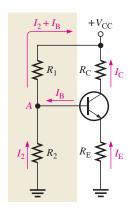

Up to this point a separate dc source,  $V_{BB}$ , was used to bias the base-emitter junction because it could be varied independently of  $V_{CC}$  and it helped to illustrate transistor operation. A more practical bias method is to use  $V_{CC}$  as the single bias source, as shown in Figure 5–9. To simplify the schematic, the battery symbol is omitted and replaced by a line termination circle with a voltage indicator ( $V_{CC}$ ) as shown.

A dc bias voltage at the base of the transistor can be developed by a resistive voltagedivider that consists of  $R_1$  and  $R_2$ , as shown in Figure 5–9.  $V_{CC}$  is the dc collector supply voltage. Two current paths are between point A and ground: one through  $R_2$  and the other through the base-emitter junction of the transistor and  $R_E$ .

Generally, voltage-divider bias circuits are designed so that the base current is much smaller than the current  $(I_2)$  through  $R_2$  in Figure 5–9. In this case, the voltage-divider circuit is very straightforward to analyze because the loading effect of the base current can be ignored. A voltage divider in which the base current is small compared to the current in  $R_2$  is said to be a **stiff voltage divider** because the base voltage is relatively independent of different transistors and temperature effects.

To analyze a voltage-divider circuit in which  $I_{\rm B}$  is small compared to  $I_2$ , first calculate the voltage on the base using the unloaded voltage-divider rule:

$V_{\rm B} \cong \left(\frac{R_2}{R_1 + R_2}\right) V_{\rm CC}$

Once you know the base voltage, you can find the voltages and currents in the circuit, as follows:

$$V_{\rm E} = V_{\rm B} - V_{\rm BE}$$

Equation 5–2

and

$$I_{\rm C} \cong I_{\rm E} = \frac{V_{\rm E}}{R_{\rm E}}$$

Equation 5–3

Equation 5–1

Then,

$$V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C}$$

Equation 5-4

Once you know  $V_{\rm C}$  and  $V_{\rm E}$ , you can determine  $V_{\rm CE}$ .

$$V_{\rm CE} = V_{\rm C} - V_{\rm E}$$

**EXAMPLE 5–2** Determine  $V_{CE}$  and  $I_C$  in the stiff voltage-divider biased transistor circuit of Figure 5–10 if  $\beta_{DC} = 100$ .

*Solution* The base voltage is

► FIGURE 5-10

$$V_{\rm B} \cong \left(\frac{R_2}{R_1 + R_2}\right) V_{\rm CC} = \left(\frac{5.6 \,\mathrm{k}\Omega}{15.6 \,\mathrm{k}\Omega}\right) 10 \,\mathrm{V} = 3.59 \,\mathrm{V}$$

So,

$$V_{\rm E} = V_{\rm B} - V_{\rm BE} = 3.59 \,\rm V - 0.7 \,\rm V = 2.89 \,\rm V$$

and

$$I_{\rm E} = \frac{V_{\rm E}}{R_{\rm E}} = \frac{2.89 \,\rm V}{560 \,\Omega} = 5.16 \,\rm mA$$

$I_{\rm C} \cong I_{\rm E} = 5.16 \,\mathrm{mA}$

Therefore,

and

$$V_{\rm C} = V_{\rm CC} - I_{\rm C}R_{\rm C} = 10 \text{ V} - (5.16 \text{ mA})(1.0 \text{ k}\Omega) = 4.84 \text{ V}$$

$V_{\rm CE} = V_{\rm C} - V_{\rm E} = 4.84 \text{ V} - 2.89 \text{ V} = 1.95 \text{ V}$

**Related Problem** If the voltage divider in Figure 5–10 was not stiff, how would  $V_{\rm B}$  be affected?

Open the Multisim file E05-02 in the Examples folder on the companion website. Measure  $I_{\rm C}$  and  $V_{\rm CE}$ . If these results do not agree very closely with those in the Example, what original assumption was incorrect?

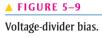

The basic analysis developed in Example 5–2 is all that is needed for most voltagedivider circuits, but there may be cases where you need to analyze the circuit with more accuracy. Ideally, a voltage-divider circuit is stiff, which means that the transistor does not appear as a significant load. All circuit design involves trade-offs; and one trade-off is that stiff voltage dividers require smaller resistors, which are not always desirable because of potential loading effects on other circuits and added power requirements. If the circuit designer wanted to raise the input resistance, the divider string may not be stiff; and more detailed analysis is required to calculate circuit parameters. To determine if the divider is stiff, you need to examine the dc input resistance looking in at the base as shown in Figure 5–11.

$V_{CC}$ +10 V  $R_1$   $R_1$   $R_C$   $R_2$   $R_2$   $R_2$   $R_E$   $R_2$   $R_E$   $R_E$   $R_E$

Stiff:

$$R_{\rm IN(BASE)} \ge 10R_2$$

$$V_{\rm B} \cong \left(\frac{R_2}{R_1 + R_2}\right) V_{\rm CC}$$

Not stiff:

$$R_{\rm IN(BASE)} < 10R_2$$

$$V_{\rm B} = \left(\frac{R_2 \parallel R_{\rm IN(BASE)}}{R_1 + R_2 \parallel R_{\rm IN(BASE)}}\right) V_{\rm CC}$$

FIGURE 5–11

Voltage divider with load.

# Loading Effects of Voltage-Divider Bias

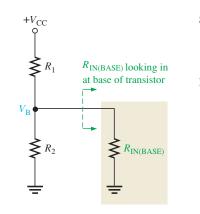

**DC Input Resistance at the Transistor Base** The dc input resistance of the transistor is proportional to  $\beta_{DC}$ , so it will change for different transistors. When a transistor is operating in its linear region, the emitter current ( $I_E$ ) is  $\beta_{DC}I_B$ . When the emitter resistor is viewed from the base circuit, the resistor appears to be larger than its actual value because of the dc current gain in the transistor. That is,  $R_{IN(BASE)} = V_B/I_B = V_B/(I_E/\beta_{DC})$ .

$$R_{\rm IN(BASE)} = \frac{\beta_{\rm DC} V_{\rm B}}{I_{\rm E}}$$

Equation 5–5

This is the effective load on the voltage divider illustrated in Figure 5–11.

You can quickly estimate the loading effect by comparing  $R_{IN(BASE)}$  to the resistor  $R_2$  in the voltage divider. As long as  $R_{IN(BASE)}$  is at least ten times larger than  $R_2$ , the loading effect will be 10% or less and the voltage divider is stiff. If  $R_{IN(BASE)}$  is less than ten times  $R_2$ , it should be combined in parallel with  $R_2$ .

## **Thevenin's Theorem Applied to Voltage-Divider Bias**

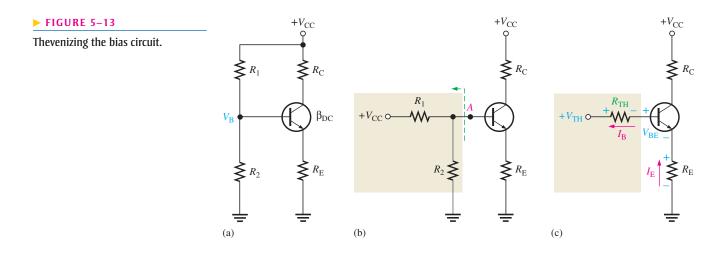

To analyze a voltage-divider biased transistor circuit for base current loading effects, we will apply Thevenin's theorem to evaluate the circuit. First, let's get an equivalent baseemitter circuit for the circuit in Figure 5–13(a) using Thevenin's theorem. Looking out from the base terminal, the bias circuit can be redrawn as shown in Figure 5–13(b). Apply Thevenin's theorem to the circuit left of point *A*, with  $V_{CC}$  replaced by a short to ground and the transistor disconnected from the circuit. The voltage at point *A* with respect to ground is

$$V_{\rm TH} = \left(\frac{R_2}{R_1 + R_2}\right) V_{\rm CC}$$

and the resistance is

$$R_{\rm TH} = \frac{R_1 R_2}{R_1 + R_2}$$

The Thevenin equivalent of the bias circuit, connected to the transistor base, is shown in the beige box in Figure 5–13(c). Applying Kirchhoff's voltage law around the equivalent base-emitter loop gives

$$V_{\rm TH} - V_{R_{\rm TH}} - V_{\rm BE} - V_{R_{\rm E}} = 0$$

Substituting, using Ohm's law, and solving for  $V_{\rm TH}$ ,

$$V_{\rm TH} = I_{\rm B}R_{\rm TH} + V_{\rm BE} + I_{\rm E}R_{\rm E}$$

Substituting  $I_{\rm E}/\beta_{\rm DC}$  for  $I_{\rm B}$ ,

$$V_{\rm TH} = I_{\rm E}(R_{\rm E} + R_{\rm TH}/\beta_{\rm DC}) + V_{\rm BE}$$

Then solving for  $I_{\rm E}$ ,

$$I_{\rm E} = \frac{V_{\rm TH} - V_{\rm BE}}{R_{\rm E} + R_{\rm TH}/\beta_{\rm DC}}$$

If  $R_{\rm TH}/\beta_{\rm DC}$  is small compared to  $R_{\rm E}$ , the result is the same as for an unloaded voltage divider.

Voltage-divider bias is widely used because reasonably good bias stability is achieved with a single supply voltage.

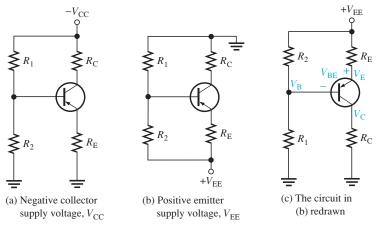

**Voltage-Divider Biased PNP Transistor** As you know, a *pnp* transistor requires bias polarities opposite to the *npn*. This can be accomplished with a negative collector supply voltage, as in Figure 5-14(a), or with a positive emitter supply voltage, as in Figure 5-14(b).

▲ FIGURE 5–14

Voltage-divider biased pnp transistor.

In a schematic, the *pnp* is often drawn upside down so that the supply voltage is at the top of the schematic and ground at the bottom, as in Figure 5-14(c).

The analysis procedure is the same as for an *npn* transistor circuit using Thevenin's theorem and Kirchhoff's voltage law, as demonstrated in the following steps with reference to Figure 5–14. For Figure 5–14(a), applying Kirchhoff's voltage law around the base-emitter circuit gives

$$V_{\rm TH} + I_{\rm B}R_{\rm TH} - V_{\rm BE} + I_{\rm E}R_{\rm E} = 0$$

By Thevenin's theorem,

$$V_{\rm TH} = \left(\frac{R_2}{R_1 + R_2}\right) V_{\rm CC}$$

$$R_{\rm TH} = \frac{R_1 R_2}{R_1 + R_2}$$

The base current is

$$I_{\rm B} = \frac{I_{\rm E}}{\beta_{\rm DO}}$$

The equation for  $I_{\rm E}$  is

$$I_{\rm E} = \frac{-V_{\rm TH} + V_{\rm BE}}{R_{\rm E} + R_{\rm TH}/\beta_{\rm DC}}$$

Equation 5–7

For Figure 5–14(b), the analysis is as follows:

$$-V_{\text{TH}} + I_{\text{B}}R_{\text{TH}} - V_{\text{BE}} + I_{\text{E}}R_{\text{E}} - V_{\text{EE}} = 0$$

$$V_{\text{TH}} = \left(\frac{R_1}{R_1 + R_2}\right)V_{\text{EE}}$$

$$R_{\text{TH}} = \frac{R_1R_2}{R_1 + R_2}$$

$$I_{\text{B}} = \frac{I_{\text{E}}}{\beta_{\text{DC}}}$$

The equation for  $I_{\rm E}$  is

$$I_{\rm E} = \frac{V_{\rm TH} + V_{\rm BE} - V_{\rm EE}}{R_{\rm E} + R_{\rm TH}/\beta_{\rm DC}}$$

Equation 5–8

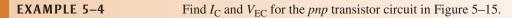

*Solution* This circuit has the configuration of Figures 5–14(b) and (c). Apply Thevenin's theorem.

$$V_{\text{TH}} = \left(\frac{R_1}{R_1 + R_2}\right) V_{\text{EE}} = \left(\frac{22 \,\text{k}\Omega}{22 \,\text{k}\Omega + 10 \,\text{k}\Omega}\right) 10 \,\text{V} = (0.688) 10 \,\text{V} = 6.88 \,\text{V}$$

$$R_{\text{TH}} = \frac{R_1 R_2}{R_1 + R_2} = \frac{(22 \,\text{k}\Omega)(10 \,\text{k}\Omega)}{22 \,\text{k}\Omega + 10 \,\text{k}\Omega} = 6.88 \,\text{k}\Omega$$

Use Equation 5–8 to determine  $I_{\rm E}$ .

$$I_{\rm E} = \frac{V_{\rm TH} + V_{\rm BE} - V_{\rm EE}}{R_{\rm E} + R_{\rm TH}/\beta_{\rm DC}} = \frac{6.88 \text{ V} + 0.7 \text{ V} - 10 \text{ V}}{1.0 \text{ k}\Omega + 45.9 \Omega} = \frac{-2.42 \text{ V}}{1.0459 \text{ k}\Omega} = -2.31 \text{ mA}$$

The negative sign on  $I_E$  indicates that the assumed current direction in the Kirchhoff's analysis is opposite from the actual current direction. From  $I_E$ , you can determine  $I_C$  and  $V_{EC}$  as follows:

$$I_{\rm C} = I_{\rm E} = 2.31 \,\text{mA}$$

$$V_{\rm C} = I_{\rm C}R_{\rm C} = (2.31 \,\text{mA})(2.2 \,\text{k}\Omega) = 5.08 \,\text{V}$$

$$V_{\rm E} = V_{\rm EE} - I_{\rm E}R_{\rm E} = 10 \,\text{V} - (2.31 \,\text{mA})(1.0 \,\text{k}\Omega) = 7.68 \,\text{V}$$

$$V_{\rm EC} = V_{\rm E} - V_{\rm C} = 7.68 \,\text{V} - 5.08 \,\text{V} = 2.6 \,\text{V}$$

**Related Problem** Determine  $R_{IN(BASE)}$  for Figure 5–15.

Open the Multisim file E05-04 in the Examples folder on the companion website. Measure  $I_{\rm C}$  and  $V_{\rm EC}$ .

### **EXAMPLE 5–5**

Find  $I_{\rm C}$  and  $V_{\rm CE}$  for a *pnp* transistor circuit with these values:  $R_1 = 68 \,\mathrm{k\Omega}$ ,  $R_2 = 47 \,\mathrm{k\Omega}$ ,  $R_{\rm C} = 1.8 \,\mathrm{k\Omega}$ ,  $R_{\rm E} = 2.2 \,\mathrm{k\Omega}$ ,  $V_{\rm CC} = -6 \,\mathrm{V}$ , and  $\beta_{\rm DC} = 75$ . Refer to Figure 5–14(a), which shows the schematic with a negative supply voltage.

Solution Apply Thevenin's theorem.

$$V_{\text{TH}} = \left(\frac{R_2}{R_1 + R_2}\right) V_{\text{CC}} = \left(\frac{47 \,\text{k}\Omega}{68 \,\text{k}\Omega + 47 \,\text{k}\Omega}\right) (-6 \,\text{V})$$

= (0.409)(-6 V) = -2.45 V

# 6–2 **TRANSISTOR AC MODELS**

To visualize the operation of a transistor in an amplifier circuit, it is often useful to represent the device by a model circuit. A transistor model circuit uses various internal transistor parameters to represent its operation. Transistor models are described in this section based on resistance or r parameters. Another system of parameters, called h parameters, is briefly described.

After completing this section, you should be able to

- Discuss transistor models

- List and define the *r* parameters

- Describe the *r*-parameter transistor model

- Determine  $r'_e$  using a formula

- Compare ac beta and dc beta

- List and define the *h* parameters

## **r** Parameters

The five r parameters commonly used for BJTs are given in Table 6–1. The italic lowercase letter r with a prime denotes resistances internal to the transistor.

| ▼ TABLE 6-1   |                         |  |  |  |  |

|---------------|-------------------------|--|--|--|--|

| r parameters. |                         |  |  |  |  |

| r PARAMETER   | DESCRIPTION             |  |  |  |  |

| $\alpha_{ac}$ | ac alpha $(I_c/I_e)$    |  |  |  |  |

| $\beta_{ac}$  | ac beta $(I_c/I_b)$     |  |  |  |  |

| $r'_e$        | ac emitter resistance   |  |  |  |  |

| $r_b'$        | ac base resistance      |  |  |  |  |

| $r_c'$        | ac collector resistance |  |  |  |  |

## r-Parameter Transistor Model

An *r*-parameter model for a BJT is shown in Figure 6–5(a). For most general analysis work, it can be simplified as follows: The effect of the ac base resistance  $(r'_b)$  is usually small enough to neglect, so it can be replaced by a short. The ac collector resistance  $(r'_c)$  is usually several hundred kilohms and can be replaced by an open. The resulting simplified *r*-parameter equivalent circuit is shown in Figure 6–5(b).

The interpretation of this model circuit in terms of a transistor's ac operation is as follows: A resistance  $(r'_e)$  appears between the emitter and base terminals. This is the resistance "seen" looking into the emitter of a forward-biased transistor. The collector effectively acts as a dependent current source of  $\alpha_{ac}I_e$  or, equivalently,  $\beta_{ac}I_b$ , represented by the diamond-shaped symbol. These factors are shown with a transistor symbol in Figure 6–6.

### Determining r<sub>e</sub> by a Formula

For amplifier analysis, the ac emitter resistance,  $r'_e$ , is the most important of the *r* parameters. To calculate the approximate value of  $r'_e$ , you can use Equation 6–1, which is derived